## ОПИСАНИЕ ИЗОБРЕТЕНИЯ К ПАТЕНТУ

(12)

РЕСПУБЛИКА БЕЛАРУСЬ

- (19) **BY** (11) **2119**

- (13) **C1**

- $(51)^6$  G 06F 7/00

ГОСУДАРСТВЕННЫЙ ПАТЕНТНЫЙ КОМИТЕТ РЕСПУБЛИКИ БЕЛАРУСЬ

## (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СИММЕТРИЧЕСКИХ БУЛЕВЫХ ФУНКЦИЙ

(21) Номер заявки: 950164

(22) 28.03.1995 (46) 30.06.1998

- (71) Заявитель: Белорусский

- государственный

государ-

- университет (ВҮ)

- (72) Авторы: Супрун В.П., Седун А.М. (BY)

- (73) Патентообладатель: Белорусский ственный университет (ВҮ)

(57)

Устройство для вычисления симметрических булевых функций, содержащее элемент СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, элемент И и элемент ИЛИ, входы которого с первого по четвертый соединены соответственно с первым по четвертый информационными входами устройства, первый настроечный вход которого соединен с первым входом элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, а второй настроечный вход соединен с первым входом элемента И, выход которого соединен со вторым входом элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, выход которого является выходом устройства, отличающееся тем, что дополнительно введены мажоритарный элемент с порогом два и мажоритарный элемент с порогом пять, входы которого с первого по четвертый соединены соответственно с первым по четвертый входами мажоритарного элемента с порогом два, со вторым по пятый входами элемента И и с первым по четвертый информационными входами устройства, третий настроечный вход которого соединен с пятым и шестым входами мажоритарного элемента с порогом два, четвертый настроечный вход соединен с пятым и шестым входами мажоритарного элемента с порогом пять, а пятый настроечный вход - с пятым входом элемента ИЛИ, выход которого соединен с третьим входом элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, четвертый вход которого соединен с выходом мажоритарного элемента с порогом два, а пятый вход - с выходом мажоритарного элемента с порогом пять.

(56)

- 1. Á.c. СССР 1767496, МКИ G06F 7/00, 1992.

- 2. A.c. СССР 1832270, МКИ G06F 7/00, 1993.

Изобретение относится к области вычислительной техники и микроэлектроники и предназначено для реализации симметрических булевых функций четырех переменных.

## BY 2119 C1

Известно устройство для вычисления симметрических булевых функций четырех переменных, содержащее четыре элемента ИЛИ-НЕ, мажоритарные элементы с порогами два и три, четыре элемента И, четыре информационных и пять настроечных входов, один выход [1]. Сложность устройства (по числу входов логических элементов) равна 34, а быстродействие, определяемое глубиной схемы, составляет  $3\tau$ , где  $\tau$  - задержка на вентиль.

Недостатком устройства является высокая конструктивная сложность и низкое быстродействие.

Наиболее близким по функциональным возможностям и конструкции техническим решением к предлагаемому является устройство для вычисления симметрических булевых функций четырех переменных, содержащее два элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, мажоритарный элемент с порогом три, четыре элемента И, элемент ИЛИ, четыре информационных и пять настроечных входов, один выход [2]. Сложность устройства равна 26, а быстродействие - 3т.

Недостатком известного устройства для вычисления симметрических нулевых функций является низкое быстродействие.

Изобретение направлено на решение технической задачи повышения быстродействия устройства для вычисления симметрических булевых функций четырех переменных.

Устройство для вычисления симметрических булевых функций содержит элемент СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, элемент И и элемент ИЛИ, входы которого с первого по четвертый соединены соответственно с первым по четвертый информационными входами устройства. Первый настроечный вход устройства соединен с первым входом элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, а второй настроечный вход соединен с первым входом элемента И, выход которого соединен со вторым входом элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, выход которого является выходом устройства. В отличие от прототипа в устройство дополнительно введены мажоритарный элемент с порогом два и мажоритарный элемент с порогом пять. Входы мажоритарного элемента с порогом пять с первого по четвертый соединены соответственно с первым по четвертый входами мажоритарного элемента с порогом два, со вторым по пятый входами элемента И и с первым по четвертый информационными входами устройства. Третий настроечный вход устройства соединен с пятым и шестым входами мажоритарного элемента с порогом два, четвертый настроечный вход соединен с пятым и шестым входами мажоритарного элемента с порогом пять, а пятый настроечный вход - с пятым входом элемента ИЛИ. Выход элемента ИЛИ соединен с третьим входом элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, четвертый вход которого соединен с выходом мажоритарного элемента с порогом два, а пятый вход - с выходом мажоритарного элемента с порогом пять.

Основной технический результат изобретения заключается в повышении быстродействия устройства для вычисления симметрических булевых функций четырех переменных. Названный технический результат достигается путем дополнительного введения мажоритарного элемента с порогом два и мажоритарного элемента с порогом пять, а также изменением межсоединений элементов в схеме устройства.

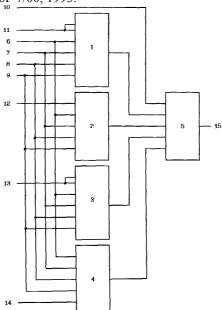

На чертеже представлена схема устройства для вычисления симметрических булевых функций четырех переменных.

Устройство для вычисления симметрических булевых функций содержит мажоритарный элемент с порогом два 1, элемент ИЛИ 2, мажоритарный элемент с порогом пять 3, элемент И 4, элемент СЛОЖЕНИЕ ПО МОДУЛЮ ДВА 5, четыре информационных входов 6, 7, 8 и 9, пять настроечных входов 10, 11, 12, 13 и 14, выход 15.

Устройство для вычисления симметрических булевых функций работает следующим образом. На информационные входы 6, 7, 8 и 9 поступают двоичные переменные  $x_1$ ,  $x_2$ ,  $x_3$  и  $x_4$  (в произвольном порядке); на настроечные входы 10, 11, 12, 13 и 14 - сигналы настройки  $u_1$ ,  $u_2$ ,  $u_3$ ,  $u_4$  и  $u_5$ , значения которых принадлежат множеству  $\{0,1\}$ . На выходе 15 реализуется симметрическая булева функция  $F=F(x_1, x_2, x_3, x_4)$ , определяемая вектором настройки  $U=(u_1, u_2, u_3, u_4, u_5)$ .

Первообразная устройства для вычисления симметрических булевых функций четырех переменных имеет следующий вид:

$F(x_1, x_2, x_3, x_4, u_1, u_2, u_3, u_4, u_5) = u_1 \oplus (u_2 \vee x_1 x_2 \vee x_1 x_3 \vee x_1 x_4 \vee x_2 x_3 \vee x_2 x_4 \vee x_3 x_4) \oplus (u_3 \vee x_1 \vee x_2 \vee x_3 \vee x_4) \oplus u_4(x_1 x_2 x_3 \vee x_1 x_2 x_4 \vee x_1 x_3 x_4 \vee x_2 x_3 x_4) \oplus u_5 x_1 x_2 x_3 x_4.$

Поясним алгоритм настройки. Известно (см. Лупанов О.Б. Об одном подходе к синтезу управляющих систем принципе локального кодирования // Проблемы кибернетики. - М.: Наука, 1965, вып.14), что произвольная симметрическая булева функция п переменных  $F=F(x_1, x_2, ..., x_n)$  однозначно определяется (n+1)-разрядным двоичным кодом  $\pi(F)=(\pi_0, \pi_1, ..., \pi_n)$ , где  $\pi_i$  - значение функции F на (любом) наборе переменных  $x_1, x_2, ..., x_n$ , содержащем ровно i единиц  $(0 \le i \le n)$ .

## BY 2119 C1

Тогда значения сигналов настройки устройства на реализацию некоторой симметрической булевой функции четырех переменных  $F=F(x_1, x_2, x_3, x_4)$ , заданной двоичным кодом  $\pi(F)=(\pi_0, \pi_1, \pi_2, \pi_3, \pi_4)$ , определяются следующим образом:  $u_1=\pi_2, u_2=\pi_1\oplus\pi_2\oplus 1, u_3=\pi_0\oplus\pi_1\oplus 1, u_4=\pi_2\oplus\pi_3$  и  $u_5=\pi_3\oplus\pi_4$ .

**Пример.** Найти сигналы настройки устройства на реализацию симметрической булевой функции  $F=F(x_1, x_2, x_3, x_4)$ , заданной посредством дизъюнктивной нормальной формы

$$F = x_1 x_2 \lor x_1 x_3 \lor x_1 x_4 \lor x_2 x_3 \lor x_2 x_4 \lor x_3 x_4 \lor \ X_1 X_2 X_3 X_4 \,.$$

Очевидно, что здесь.  $\pi(F)=(\pi_0, \pi_1, \pi_2, \pi_3, \pi_4)=(1, 0, 1, 1, 1)$ .

Тогда сигналы настройки устройства определяются согласно приведенным выше формулам следующим образом:  $u_1$ =1,  $u_2$ =0  $\oplus$  1  $\oplus$  1=0,  $u_3$ =1  $\oplus$  0  $\oplus$  1=0,  $u_4$ =1  $\oplus$  1=0,  $u_5$ =1  $\oplus$  1=0. Следовательно, сигнал логического нуля должен быть подан на настроечные входы 11, 12, 13 и 14, а сигнал логической единицы - на настроечный вход 10.

Достоинством устройства является высокое быстродействие, которое составляет  $2\tau$ , где  $\tau$  - задержка на вентиль (быстродействие устройства-прототипа равно  $3\tau$ ). Дополнительным достоинством является низкая конструктивная сложность устройства, которая (по числу входов логических элементов) составляет  $2\tau$ , в то время как сложность устройства-прототипа равна  $2\tau$ 6.

Составитель Е.В.Федоров Редактор Т.А. Лущаковская Корректор Т.Н. Никитина

Заказ 0063

Тираж 20 экз.

Государственный патентный комитет Республики Беларусь.

220072, г. Минск, проспект Ф. Скорины, 66.